|

|

| ||

|

Shopping Cart

|

| Home | Products | Teensy | Blog | Forum |

|

You are here:

MP3 Player

|

|

|

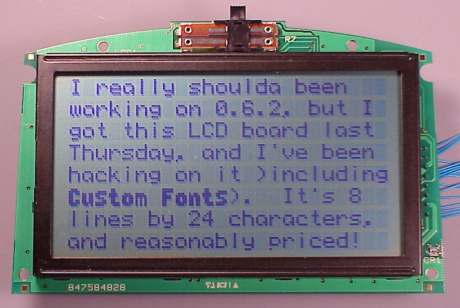

HistoryDecember 28, 2001: I have (finally) set up aDecember 17, 2001: It's official, firmware release 0.6.4. It's been quite some time since the last release and a lot has changed. This code should be much more stable than all the previous 0.6.x versions. I also added some minor features back to the old non-SIMM version (now 0.1.3), so it's auto-detect IDE master/slave and will work with those older buggy drives. Please give 0.6.4 a try. Your feedback, tested with your hard drive and your SIMM, would really help. As usual, I'm behind on answering emails. Now that this firmware release is out, I'll try to catch up tonight and tommorrow. December 14, 2001: I did more work in the firmware and FPGA over the last couple days, and it is now committed to CVS. Dave's snapshot page should have it soon. Here's a compiled image with all these changes.

The other interesting thing that happened today was a discussion on the SDCC developer mail list (which I am involved with). SDCC generates very inefficient code for initializing static and global variables. It's looking like this will improve soon. December 12, 2001: Last night I worked yet again on the DRAM controller, this time on the 8051-interface section. I redesigned the address latching circuitry (using the 8051's ALE to enable flip-flops instead of using it as a clock). This appears to greatly improve the stability of the player. My test board has been running for a little over 11 hours continuously since I made this change. These "hardware" changes are inside the FPGA, so your board will get these changes when you upgrade the firmware. No physical changes are made to the board, and the changes will work on all three board revisions. I committed this new DRAM controller to the CVS server this morning, so Dave's nightly build page should have a compiled image with the new DRAM controller sometime tommorrow. (I'll put a copy on the yahoo group so you can get it now). Please give this new code a try and let me know if it is stable or crashes on your board. It's still too early to tell for sure, but it's looking pretty good. The board I'm using now is the worst one I have... it's never managed to run any of the 0.6.x firmware for more than a 4-5 hours, and with this new code it's been playing without problems since I made the change 11 hours ago. Tom also committed a large group of cleanups and improvements to the code, mostly in the display and non-volatile parameter handling. There will probably be some more fixes over the next couple days. I am particularly interested in integrating Dave Johnson's idea to allow full max volume output while still having the tone controls. If things are looking stable, I'll make an official release (probably 0.6.5) sometime during the weekend. If you've been following the yahoo group discussions, you've probably seen talk about officially ending the display beta test. The display firmware seems to be very stable. The display bugs appear to have been completely solved by the changes I committed on August 8th. Tom added several new features to the display board's firmware in August and September. The last bug was fixed on October 7, and there have not been any changes since. All displays that have been shipped in November and December have the latest firmware and do not need an upgrade. Robin and I are planning to send free display upgrade chips to everyone who has the original display firmware. This upgrade will fix the shift-by-two-pixels bug and other minor pixel corruption, and it'll also update the display with all of Tom's performance enchancing code, which greatly reduces the flicker when the screen is redrawn and reduces the bandwidth used on the serial port. I'll post details when we're ready to send the chips. We're planning to have a special page with a form to request the chip (since many people's addresses may have changed). PJRC will pay for the chip and shipping via low-cost postal mail for everyone who has the old firmware. December 11, 2001: Today I spent quite a bit of time investigating some bugs reported by "Marco", who apparantly is attempting to add cdrom support to the code. He ran into all sorts of strange (and fairly reproducable) problems. He didn't send a copy of his code, but after a while I managed to reproduce the problem and ultimately get to the bottom of it. I was hoping this might lead to a fix for the current bug that causes the firmware to crash after some time, but Marco's problems turned out to be related to some tricky aspects to using 16 bit PIO access to the IDE interface. The current firmware only uses PIO access as startup. I added some description of the 16 bit PIO issues to the memory map page. December 10, 2001: It looks like subscribers are started receiving the January issue of Poptronics, which includes an article about this MP3 player project. The article shows the rev A board, as the new rev C board was not ready in time for their publication deadlines, and rev B wasn't documented well enough for the article. All three revisions to the board have made improvements to the power supply, while the MP3 player part has remained the same. If you're a Poptronics reader and you plan to build this project, please use the newer rev C design, which makes some significant improvements to the power supply section. Rev C printed circuit board artwork and assembly instructions are on-line. Saddly, I have not had time to draw a nice schematic for the new rev C board, but I do have a hand-drawn schematic of the new power supply section, so I'll get that scanned soon and put it on-line (and eventually draw a nice schematic like the other ones). If, for some reason, you really want to build rev A, don't forget to check the Rev A Errata page. The Poptronics article probably doesn't mention these errata items, which is entirely my fault. November 4, 2001: This weekend PJRC.COM moved to new hosting at Verio. The new server has a lot of bandwidth, so pages should load much faster for anyone with DSL, cable or other fast internet access. Dial-up users may even notice an improvement at busy times. Hopefully the days of DSL users bringing the site to its knees with Teleport Pro will soon be a distant memory. Verio should also be much more reliable that our old ISP (inetarena.com), who's had many outages and performance problems since its founder sold the company to netrover.com. The DNS was switched Saturday afternoon, and since then the new server has slowly been taking more of the traffic. A few people are still accessing the old server. If you're seeing this message, your nameserver has updated with the new IP number and you're accessing the new server. Our email was down for part of Friday and Saturday, so if you sent Robin or me a message and it bounced, the email should be working again. CVS is still not loaded on the new server, but it should be running sometime tommorrow. I'm hoping to wrap up all this server transition stuff Monday night and spend the rest of the week working on much-needed updates to many of the web pages. Moving the entire website and getting everything to work again has been quite a bit of work over the last few days. It's quite possible I missed something. If you notice anything broken, please send me an email. We have several more assembled boards and unassembled kits available. We actually ran out of kits in the middle of last week and the last assembled board from the first batch was shipped on Friday. The good news is that we've got several more in stock just in time! October 29, 2001: We've finally cleared all the backorders for mp3 player boards and kits. There's actually a few rev C boards and one kit left at the moment, and we're no longer reserving them for people who selected Western Union or PayPal but haven't responded to emails over the last week. It feels great to finally be caught up! We'll have the next batch of boards ready on Nov 5, so if we run out this week it'll only be until next Monday. This weekend I created the Rev C kit assembly diagrams. At the bottom of those pages is a download for a hi-res copy of all 12 assembly diagrams, which looks good when printed on a laser printer. This time, I put some extra work into getting all the parts very clearly labeled with bold text and all the other parts nicely gray'd out to make it easier to read, even when printed without color. If you're one of the people who's recently received a Rev C kit, please contact me if anything is unclear in these diagrams. Robin and I both double checked them, but it is always possible I could have made an error or omission. The Rev C layout artwork is also on-line. I'm still working to update the schematic for Rev C, and hopefully it will appear sometime this week. I also have the images ready for a schematic and layout of the pushbutton adaptor board that comes with the display. I know several people have requested this... it will be up very soon. I'm trying to fill in the missing web pages (here and on other parts of the web site) over the next several days. Once these are written/drawn, I'm planning to get back into working on the firmware in a serious way. We've been in contact with Gernsback Publications very recently, and it looks like they will run a story about this little mp3 player project in the January issue of Poptronics Magazine (formerly Popular Electronics). The material in the magazine will cover the Rev A board, since we didn't have all the info needed for Rev C in time for their deadline. The story in the magazine won't have much that isn't already here on the web site, but it should be able to reach a lot of folks who don't know about the site. I'm told that the January issue hits the news stands on December 11, a couple weeks before Christmas. If you want a copy, that'd be a good time to look for it. I'm told that the mp3 player will appear alongside some antenna project on the cover of the magazine. We sent them a board to take photos, but I do not know exactly what they will do. We are planning to increase the price of the unassembled kit and the display, but only slightly. Don't panic... nothing has changed yet, and nothing will change until at least November 15 to allow anyone who's "thinking about it" to order at today's prices. The unassembled kit will go to $150, which is the same price as the assembled and tested board. The main reason for this is because we spend a similar amount of time putting the parts into the nicely labeled bags as we do putting them into the circuit board, but the tech support on kits is much harder. On the display, we're going to increase to $42 (adding only $5). This is my fault... I underestimated the cost of building the custom cables, particularily the ribbon cable that needs to be hand soldered on all 17 conductors. All the other parts will remain the same price, at least for the forseeable future. Well, that's a bunch of things for one news update. I think that more or less covers everything. Now that we're finally caught up on these mp3 players and the 8051 development board, I'll be doing some much-needed updates to the web site and then quite a bit of work on the firmware. October 21, 2001: We finally have the first small batch of Rev C boards and kits ready. Here is the photo of the first Rev C board:

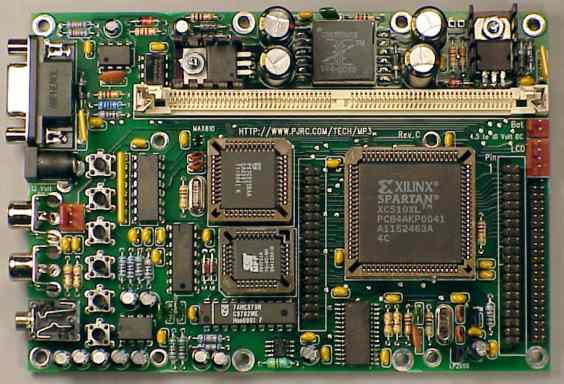

Here is a larger photo (120k). We'll be shipping boards and kits tommorrow, and this first small batch should cover most, if not all of the backorders. I'll be posting info about the new rev C to the technical docs section over the next week, but for now Robin and I are tired and need to take a little break! October 10, 2001: Well, I've missed the deadline to get the first 20 rev C boards made by Saturday (Oct 13), but it looks very good for getting them sometime next week. One really positive thing that's come out of this long process is that I've finally drawn a reasonable schematic for the first board. Well, it's missing the pushbuttons and serial interface, but that'll be easy to add. Getting all those connections checked was a lot of work, as you can see from that image. I know there's a good number of people (several are students) who've been waiting for the schematic for quite a while, so enjoy. Rev C makes only a couple minor tweaks to the main schematic, so it'll be relatively easy to get a complete rev C schematic up by the time we're shipping boards. Also, I should mention that I've fallen behind in answering emails (worse that usual...) Please be patient, I will try to answer them all, probably next week while the boards are getting fabricated and we're making the inevitable last-minute orders for a few missing parts. October 4, 2001: It probably seems like I've dropped off the face of the earth... no updates to this page, not much happening with the firmware lately, ran out of mp3 player circuit boards, etc. Well, here's a bit about what's been going on lately. We ran out of boards about 5-6 weeks ago, and once more I was faced with the decision, "should I just make more of the exact same board, or should I try to improve the design". As you may know, I've never been 100% happy with the power supply part of the board. Rev A worked, though not nearly as efficiently as I wanted. Rev A also has a 4.5 to 6 volt input, and it was easy to damage the board by applying more than 7 volts to this input. I made some minor changes to create rev B with a sturdy 6 to 10 volt input (in addition to the 10-15 volt input), and the change reduced the heating in the TIP102 transistor. Still, it seem like it ought to be possible to do better. Well, it isn't easy. Over the last several weeks I've made multiple attempts that turned out to be dismal failures at a better power supply. I was about to give up. I took one more shot at it, and finally a result that I think is pretty good has come about. Here's a photo of the prototype:

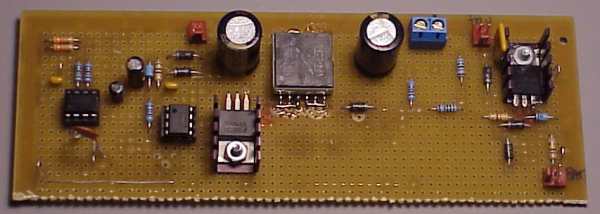

This supply uses a lot of the same parts as rev B, but the performance is considerably improved. The higher voltage input is still 10 to 15 volts, with protection from the nasty spikes from a car's alternator. The low voltage input is now 4 to 10 volts, which means rev C will be able to run from four AA batteries like rev A, but will be sturdy like rev B. Rev C's battery input will be much more efficient that either rev A or rev B... I wanted to be close to 100% efficient, but that's nearly impossible for a supply that can step up or step down as needed. I made many attempts to get really high efficiency, some using lots of expensive parts, but in the end none worked really well. I talked with a guy who's an expert at switching power supplies, but all his ideas revolved around complex custom transformers and inductors. I tried contacting some of the companies that make these. Most won't touch it for under 5000 parts/year, and those that will are very expensive for qty 100-200. So it looks like the standard parts (Cooper/Coiltronics) will have to do. I think this rev C supply is a good compromise and it keeps the cost and total size about the same as rev B. One of the major changes is a new PWM control chip. This new part (TL5001) includes a sort start limiter, which will eliminate the problem were the board can trip the current limiting that's built into many lab bench power supplies (not an issue for batteries and "wall warts"). The new switching supply makes only +5 volts, and a LP2950 linear regulator makes the 3.3 volts. Creating only +5 volts allows the supply to make better use of the transformer, and I switched to a somewhat smaller transformer (less magnetic material = lower losses is the core, which more than makes up for the small loss in the LP2950 for 3.3 volts). I also did a little trick to use the flyback voltage to create a little higher drive voltage for the mosfet, which really helps reduce the heating in the mosfet (and improve efficiency) when the supply is run from only 4 volts. There's also an undervoltage lock-out and a max duty cycle limiter so that the supply acts much more gracefully as the battery voltage falls below 4 volts. I also overhauled the circuit that muxes the 12 volt and battery inputs and protect from car alternator noise while preventing the battery from seeing destructive overcharging. The rev A and rev B versions used a diode in series with the battery, which really cuts into the battery's run time. The rev C design uses a P-channel mosfet (it's on the bottom of the prototype board) to eliminate the loss from that diode. I think that's most of the changes... all in all, it's quite an improvement over rev A and rev B. Though not as ambitious as my first couple (failed) attempts, I think it's pretty good and it'll fit into the existing board size without changing the cost of the board much (we'll keep the price the same at $150). A major frustration in this project has been the CAD software. The program I used for rev A and rev B is having a lot of trouble (corrupted files, bogus gerber output, etc). It really sucks to have to redraw an entire board with this many connections, but that's exactly what I had to do. Luckily I have access to some better software now, which has its own set of minor problems, but at least it seems to have a solid database and file format behind it. I'm going to avoid mentioning names, but I will say that the really problematic program was one of the really inexpensive packages. I guess you get what you pay for... So the big question is when will these rev C board be available. I wish I had an exact date. Today the new transformers finally arrived. We're still missing some of the important parts, but have a small number of them left over from rev B. I talked with the board fab company and they can get us a small number of boards in a hurry (for an extra fee, of course). We're going to try to get the first rev C boards and kits shipped on Oct 15. I know we have a few folks waiting who're using the board as part of a project with an urgent deadline. We're going to try to ship to them and the people who've been waiting more than 2 weeks. We'll get the rest of the boards and have them built later in the month... so hopefully we can have all the backlog taken care of before Halloween (Oct 31). I probably won't manage to get much done on the firmware until the boards and kits are sitting in stock and all the orders are shipped. One exception to this is the display beta test. Tom did a lot of work on the display firmware a couple months ago, and I made some small changes to fix the 2-pixel-shift bug and other random drawing bugs. Tom's new code includes some changes to make the display update better with less communication bandwidth from the player, but there's one more bug in this new code that prevents it from really improving the redraw responsiveness. Tom has been on a vacation for a couple weeks but recently returned. He'll probably look into this soon, and either way I'll do some work with the display firmware so that when we have the board again later this month, we'll have displays with the new debugged and improved code on them (the display is not easily upgradable like the player is). So that's more or less where the project is at. I am alive and well, but quite busy trying to get everything put together to finally have rev C boards available. Hopefully next month we'll have plenty of boards again and I can get back to working on the firmware and doing much-needed updates to the web site. August 24, 2001: It's been a few weeks since I've added any updates here. I'm going to try to get an update up here at least once a week. It's been almost exactly 2 months since the firmware development was moved to CVS, and during that time several people have come on board and really helped fill out a lot of the player's features. Ian did quite a bit of work to add items to the display, including interactive tone controls. Zach added code that scans all the directories on the drive. I overhauled the device drivers to speed this up, and Matthew has done quite a bit of work to optimize this. He also began some of the initial coding to be able to read .m3u files, but much remains to be done there. Matthew also made several valliant attempts to make that code non-recursive (allowing almost limitless subdirectory depth to be scanned), but that's a difficult task. I did some optimizing and improved the recursive version, so we can at least scan 5-6 levels deep. Somewhere in there I spent a very frustrating week or so chasing after the bug that makes the player lock up eventually, but it still ellludes me. Early on, Ian had written some code to find ID3 tags. I fixed a couple bugs, and then Ian, Chris, Matthew and others did quite a lot with ID3 tags, and today's firmware displays the ID3 info on the LCD. Zac joined the group and fixed a long-standing bug in my I2C driver code. Zac then added an nice elapsed time display, where "--:--" had always been, and he did some cleanups and improvements to the ID3 parsing code. Matthew did some more work to try to process .m3u playlist files, but this really needs more support from the drivers. I added a driver function to allow memory mapping 4k sections files, but more library-level support is needed for parsing before .m3u processing can happen in a reasonable efficient manner. Chris added more play modes, sequential in just one directory or the whole drive, random in directory or whole drive, etc. Chris also added a resume feature, where the player will usually remember where it was in the list and start there again when it is used again after a shutdown. Tom has been working on adding some cool features to the display board code. I did some testing and fixed the shift-by-two-pixels bug in the display, and Tom has added a freeze/unfreeze feature that should make updates flicker less. Tom also put in support for scrolling directly in the display, which will cut down on the excessive data trasfer to the display. I believe this is most of what's happened in the last month, but it's hard to recall everything in detail... If I've missed something that anyone contributed, please let me know. So what's next? Well, it's becoming clear that soon there needs to be a new official firmware rev, even if we can't call it "stable". In firmware development, probably the next major thing will be an overhaul of the main playback state machine. This is no small task. Eventually this would enable playing files larger than the SIMM, and probably also use the avaialble memory better, perhaps to read ahead into the next file if there is a lot of memory, perhaps to read the first part of many upcoming and/or previous files to have rapid response to the pushbuttons. There's also the task of reading .m3u playlists, ID3v2 tags, fast forward/rewind, more LCD stuff... the list goes on and on. Actually, there is a file in the firmware source called "wish_list.txt" which is more or less the official list of requested features. This list is writable only to developers with CVS commit access, mainly so that ideas are filtered through developers who have an idea of what is and isn't feasible. All developers are welcome to add to the list (or remove as things are implemented). On the less technical front, we ran out of circuit boards a few days ago. We're working to get more made, but it will be a couple weeks. It'll also consume some of my time, so I won't be doing as much work on the firmware until they're done. The final thing that's going on it pjrc.com will be moving to a different ISP. There will be a couple weeks of overlap, so with some luck things will go smoothly with the DNS and there won't be any down-time (I hope). The new server will be at a data center with very high speed connections to the net, so viewing pjrc.com should become noticably faster if you have a broadband internet service. It should also be much more reliable that what we've been using. August 5, 2001: Today I spent the whole day writing a dir_read_fast function which is an attempt to make a much faster directory read. If you've tried 0.6.3.3 or the recent CVS versions, you know that they scan all the subdirectories on the drive (up to some level, currently 3 deep in today's CVS code). Today this is slow. This new fast directory read should make a big difference. Right now it's very new and not used by the directory scanning code (it's API is a bit different). Also, if you haven't been keeping up with the latest CVS code, about a week ago Matthew and Ian got ID3 tag display working. All of the 8 lines of the display now do something. I want to make an official release on the firmware page, but it will have to wait as I spent the entire day doing the new fast directory reading code. July 25, 2001: Quite a bit has happened in the last 24 hours! I haven't had much time to work on the project for the last few weeks, and the firmware hit a limit called DSEG overflow which prevented anyone from doing much. A couple days ago I wrote a perl script that checks the DSEG usage and I made a bunch of small improvements to make more DSEG space. Matthew added display of which directory is being played. Ian committed some bug fixes. Quite some time ago Ian wrote code to read the ID3 tag, but until last night it wasn't finding the correct place in the file. I fixed that, and then Matthew picked it up and added parsing and display of the ID3 tag info (title, album, artist). There's been some fiddling with optimizing the directory scanning code, and it was broken for a while but looks like it may be fixed now. Things are really moving. If you want to try out this cool new stuff, grab the source code from CVS, or download from Jim's automatically updated compiled images. If there aren't any major bugs, I'll make rev 0.6.3.4 over the weekend. June 30, 2001: Zach added code that plays all the MP3 files on the drive, not just the root directory! Ian added adjustment of the bass and treble roll-off frequencies. I've been quite busy lately had haven't even been able to keep up with my email and the yahoo group. Today I included Zach's new code. I probably won't have much time for this project until July 4. If you've sent me an email and I haven't answered, please try to wait until the 4th to remind me. June 26, 2001: I stayed up late and did some investigation into why some newer SIMMs are incompatible with the player. The short story is that there is both good news and bad news. First, the good news is it looks like I'll be able to improve the SIMM detection code to make these newer SIMMs work properly. But, the bad news is that the hardware was designed around the older style of SIMM and only a portion of newer SIMMs will be usable with the player. Here are some photos of both types of SIMMs. I have an archived copy of the datasheet for the older SIMM type. When I designed the board, this was the only datasheet I could find on-line. The four chips on that newer SIMM shown below are Samsung KM48C8000, and I was able to find someone's old copy of the datasheet (google is great!). Using the datasheet for the chips and some reverse engineering with an ohm meter, I was able to learn a bit about these newer SIMMs. Using today's firmware (0.6.3.2), this newer 32 meg SIMM is detected as 8 megs, and the player attempts to use it and crashes (because only 4 megs is actually usable).

The devil is in the details, and I'll describe what's going on a bit. 72 pin SIMMs have a 32 bit data bus. The bus on the player is only 16 bits, so the board connects the upper and lower 16 bits together and then tries to tell the SIMM to only read/write 16 bits at a time. SIMMs have four row control lines, four column control lines, and between 10 to 13 address pins. DRAM memory is arranged in a matrix. Other easy-to-use memories like SRAM and EPROM are also built this way, but you can't "see" the arrangement because there is some nice circuitry inside that takes care of those details. With DRAM, you have to deal with the arrangement of the matrix inside. This is where the row and column lines come into play. To access a particular memory location in a single DRAM chip, you have to specify the address in two parts. First, you drive the address pins with the number of the row you want and assert the row control pin. A short time later (68 ns on this board), you drive the address pins with the column you want and assert the column control signal. There's also a write enable bit. If it's high when the column control was asserted, the DRAM sends data to the player, and if was low it stores whatever data the player drove onto its data pins. This sequence of events to access the DRAM is done automatically every time the processor reads or writes the memory and also when one of the DMA channels needs to read. There is also another type of operation called refresh, which happens every 15.6 µs. When multiple DRAM chips are assembled together on a SIMM, there are several of these row and column control lines that are brought out to the pins of the SIMM, and therein lies a good portion of the issue at hand. To be specific, there are four row control lines, labeled RAS0, RAS1, RAS2 and RAS3, and four control lines labeled CAS0, CAS1, CAS2, and CAS3. On the 32 meg SIMM, each RAS line controls 4 megabytes that occupies 16 bits of the data bus, and for each 4 meg RAS-controlled section, two CAS lines control each half to allow 8 bit wide access. If that last sentence was confusing, here's a nice diagram (which might be even more confusing :)

The mp3 player board uses the four RAS lines to enable one of the four 16-bit wide sections. It always asserts all four CAS lines at the same time (I ran out of FPGA pins and the chips that didn't get RAS asserted will ignore it). Using address pins A0 to A10 (as shown in the diagram) twice (row and column), there are effectively 22 address bits sent to the SIMM. Two of the address bits from the processor (or DMA) determine which of the four RAS lines gets used, for a total of 24 address bits. That's 16 million, and because two bytes are transfered at once, it all adds up to 32 megs of usable space and works quite nicely. Well, that's the way is was. Somewhere, somebody changed the way SIMMs were made, and many newer SIMMs are connected in a very different way than that diagram shown above. I don't have a similar diagram for the newer SIMM, because I haven't found any datasheets on these newer SIMMs and I didn't draw a diagram (special thanks to Micron, by the way, for that nice diagram and at least keeping their data sheets on line... without Micron I would never have been able to figure out how to do this project!) The newer SIMM uses only RAS0, and RAS0 controlls all 32 bits (instead of just 16 like the older SIMM). RAS1, RAS2 and RAS3 are not connected to anything at all! Worse yet, it uses 13 address lines instead of 11, where all 13 lines are used during the row selection but only 10 are used to select the column. The other three lines do nothing during column selection, but they are needed for the row. The sad truth is that the mp3 player board has 11 address lines, not 13 (there are no more pins available on the FPGA). It has 4 row select lines, and three of them are useless of this type of SIMM. There is only a single column select line that is connected to all four CAS signals, so when the player writes to the SIMM, it will actually be storing 16 bits of data into both the upper and lower 16 bits of the SIMM. Using only one RAS line, 11 bits during the row select and 10 bits during the column select, there's only 21 effective bits of address info, which gives 2 million 16-bit wide memory locations, or 4 megs. It's unfortunate that there's 32 megs of memory on there, but due to the board design and the SIMM's arrangesment, only 4 megs is usable. Of course, today the firmware incorrectly concludes that it can use 8 and then crashes, but at least that can be upgraded to check more carefully which parts of the 32 meg address spaces it can "see". Frustrating, but I guess it's better to know what's going on and at least be able to do something rather than have the code end up completely incompatible with these SIMMs. There appear to be many other arrangements on the newer SIMMs. For example, if this board were populated with KMC48C8100 chips (instead of KMC48C8000), it would still be a 32 meg SIMM, but 8 megs would be usable instead of 4 megs. On a simm like this, it possible to disconnect the RAS pin from two of the chips and connect them to RAS2 on the simm's edge to double the amount of memory the player can use, but there's nothing that can be done about the extra row address lines. If you're shopping for a 32 meg SIMM to use with this board, be sure to look for the older style, which almost always has 16 or 18 chips (8 or 9 per side), where each chip has 24 pins in four groups of six. The older 8 meg SIMM look similar, but the chips are 20 pins in four groups of five. June 26, 2001: I just posted a new firmware rev... the first one made within CVS. There's new DRAM controller in 0.6.3.2 that might cure the problems that recent firmware has had on the rev A circuit boards. More comments about what's changed are on the firmware page. June 25, 2001: CVS is finally set up. It looks like it's working pretty well. The commands you'll need to access it are on the firmware page. Tom committed file_uncache to CVS !! Tonight I commited some code that Zach sent in an email. Zach's code is a first attempt at reading in the subdirectories and files within them. It just reads the directory and prints them, but it does manage to recurse into each of the subdirectories. June 24, 2001: If you haven't been following the yahoo group, it's looking like 0.6.3.0 is much more stable than the 0.6.2.x revs. I've spent an unbelievable number of hours chasing after this bug, probably more than I spent writing most of the code, and now that it's fixed I'll be able to work on adding cool features (or adding low-level support for others to add cool features). There's still a couple lock-ups that can occur, mainly if the IDE drive doesn't respond (need to add retries). Still, the 0.6.3.x firmware is much more stable, so if you've got 0.6.2.x on your board, it's probably a good idea to upgrade. Today I fixed a problem with the makefile, and I changed the build process a bit to eliminate the binary files. Those changes are really to prepare for a transition to using CVS, probably within the next few days. The changes really only effect developers, who should grab 0.6.3.1. If you installed 0.6.3.0 from the image file (not source), there's no need to upgrade if you're not hacking on the code. Also, I heard from Tom today and he's getting close to having file_uncache written. That's a really big deal, because this function is the key missing piece to being able to do some much-needed features, like playing files larger than the SIMM and keeping the first 50-100k of several files cached so that the next/previous buttons respond rapidly without waiting for the drive to spin up. This is very exciting news. June 23, 2001: Ian did quite a bit more work on the navigation for the user interface. It's only partially written, but you can really see where it's headed. I did some more work with the DRAM controller and the new version seems to improve the stability, but it's still not perfect. On a whim, I up'd the rev number to 0.6.3.0. I've been working a bit with CVS and reading Karl Fogel's CVS book to make sure I really understand it. I'm hoping to move the development to CVS in about 1 week. June 21, 2001: Yesterday I made some additions to the display code, and today Ian began the process of converting to the new display scheme. There's a couple new revs on the firmware page. June 19, 2001: I did more hacking on the DRAM controller and finally put in that better bus arbitrator I've been planning for a long time. I actually did much of it over the weekend, and a miracle happened this evening... it worked perfectly on the very first try! It allows the DMA to get a lot more access to the DRAM than before, and it still provides a rapid response to the 8051 bus cycles by locking out any new DMA operations for 31 cycles after the 8051's PSEN fetches an opcode that could be a MOVX (access to DRAM). The new rev (0.6.2.E) also includes Ian's latest code which uses the upper right button to select which parameter to edit, and all are edited with the INC/DEC buttons (which frees the arrow button for upcoming navigation features). Andy sent a small patch to one of the utilities that allows it to work under windows (using cgywin), so there may be a day when development can occur on Microsoft systems. June 17, 2001: Ian did some really cool coding for the display to make a scrolling filename and a nice "slider" display of the volume setting. I just merged Ian's changes into the firmware (new rev on the firmware page). I also added low level support for the tone controls and timers. June 13, 2001: I spent another long session working on cleaning up the remaining stability problems in 0.6.2.x, and there's yet another new rev on the firmware download page. I added a timeout check inside the serial port transmit routine. If for some reason the serial port output ends up in an infinite loop waiting for space in the output buffer, it will automatically reset the port and clear the buffer. This was one of the last places where an infinite loop could occur. The other change involved hacking on the DRAM controller. Before I get into the details, I should mention that this "circuitry" is all soft configured inside the FPGA chip, so all you need to do is install the new firmware and your board will get this new circuitry. There are no changes to the physical hardware. These changes will work on all existing boards, either rev A or rev B. The crashes seem so random that I've been worried that perhaps there may be a slight timing problem inside the DRAM controller. There are four things that compete for access to the SIMM. These are the 8051, the two DMA channels, and the DRAM refresh timer. The IDE interface shares resources with the SIMM (mostly due to using the hobbist-friendly 84 pin PLCC package chip instead of the less-expensive 144 pin TQFP fine pitch surface mount version). However, it works out that the IDE interface can use the same bus arbitration as the DRAM because its use is only from two sources, the 8051 and the IDE->SIMM DMA channel. So, I was worried that perhaps a 8051 bus timing problem may sometimes occur if the DRAM was previously in use by one of the other sources and the access made on behalf of the 8051 starts later than normal. This is really a long-shot, but I've been over just about every other part of the project a dozen times, so why not fiddle with the FPGA too! I ended up designing a very paranoid circuit that watches the 8051 bus as it fetches instructions from the flash rom. There are six bytes that are the opcodes for the MOVX instruction, which is the only 8051 instruction that can access DRAM. The current firmware only uses two of the six opcode (@DPTR, but not @R0 and @R1). Still, I made the circuit generate a pulse just after PSEN latches a fetch of any of these six bytes. This pulse resets a count-up-and-hold counter for 32 cycles. When this little counter is at any state other than the hold (31 cycles following the PSEN-driven fetch of any of those six bytes), the bus arbitrator locks out any DMA or refresh access. This makes it absolutely certain that the control state machine will be in the idle state when the 8051 asserts either its RD or WR pins, which means that the DRAM access sequence will always begin with the exact same timing relative to the falling edge that starts a read or write. Of course, the opcode fetch may have been an operand instead of an opcode (or the MOVX address accesses a register in the FPGA and not the SIMM), in which case access to the SIMM is locked out needlessly for 31 cycles. Fortunately, that doesn't happen much and the performance hit is very slight. I did quite a bit of work measuring the timing relationships of the 8051 and DRAM signals with my Tek 475 oscilloscope (with BTW, Robin picked up for me on E-Bay for Xmas :) The normal timing put the CAS pulse in the middle of the 8051's RD, so the data is certainly being delivered to the 8051 with plenty of timing margin in the normal case. With this new DMA lock-out circuit, that case is certain to happen every single time, as no other access can begin for 31 cycles after the opcode fetch that preceeds the 8051 asserting RD or WR. I have no idea if this has actually lead to any of the instability of the firmware, but it's in 0.6.2.C, and my board has been running for about 7 hours without a lock-up since I made this change (and the timeout in the serial port transmit wait loop). The previous revs also ran for hours in initial testing, so it's still too early to know if either of these changes really fixes the lockups. June 10, 2001: Today I put quite a bit of time into trying to fix the last bug or two in 0.6.2.A. I played with the DRAM controller quite a bit, and there's a new rev on the firmware page. I haven't had it lock up in many hours of testing, but it's still too early to know if it's really stable. I also did some preliminary work on a nice malloc and some groundwork for eventually having subdirectory/playlist support. There's some discussion about it on the yahoo group. 0.6.2.B has two new files, malloc.c and playlist.c, which aren't used by the rest of the project at all, but they are sort-of some planning for how things will eventually be done to provide playlists. If you've been waiting for the laptop drive standoff set, it's finally an orderable part now. There's a photo on the page showing exactly how it mounts the drive to the circuit board. June 9, 2001: I've been working on the firmware this morning and afternoon, and there's yet another rev on the firmware page. This rev adds storage of the volume and random play state into non volatile memory. Several bugs are fixed, but there's still one or two left causing infrequent crashes. I want to get this set of features stable before going after really complex features like subdirectories/playlists, sophisticated LCD navigation, etc. Robin and I are working this weekend to get more of the beta test LCD boards built. If you're one of the few people who didn't get one, we're working on them and they should ship on Monday, June 11. Here's the page for ordering the beta test display. We've also got those standoffs that are the right size to fit most laptop drives. We should have a page to actually order them, sometime later this weekend. During these last few weeks of working on the display board and related firmware, I've fallen pretty far behind on answering emails. I did a couple long sessions in the last couple days. If you have a really urgent need, please put "URGENT" at the beginning of your subject line. June 7, 2001: After a long night of debugging, many of the bugs in the C version are fixed and it's much more stable. I added back support for all of the 6 pushbuttons on the board, and most of the other things that were in 0.6.2. I want to get to a stable version that does everything 0.6.2.1 does, and also stores the random seed and file position in non-volatile memory. I really want to have a stable version before making major changes for things like playing files larger than the SIMM, reading subdirectories, menus on the LCD, etc. June 3, 2001: Robin and I spent quite a bit of time this weekend building those beta-test pushbutton boards. Robin soldered most of the pushbuttons! We had more adventerous souls wanting beta test boards than I originally anticipated. It looks like we'll have some extra boards after Monday, but we'll have to make a few more of the ribbon cables for them sometime during the week. Tonight I put quite a bit of work into the firmware, and a new rev is on the firmware page. It adds a new serial input parser that's mostly converted to C. I originally tried to put the parser into the interrupt routine, but it was quite a bit of code and CPU time and somewhere there was a bug or two I couldn't seem to fix. Ultimately I went with the conventional approach of buffering the raw input and putting the parser into the main program (in C) and that's working quite well. Three of the new pushbuttons are supported, but it will be a lot easier to add support for the others now that the parser and interrupt driven serial I/O are working together well. May 31, 2001: We finally have some beta test display boards ready to ship. Here is the page to order a beta display. At the moment there's just a few, but I'll build up some more this weekend. As you can see, the pushbutton board is hand-built and it takes some time. The display board has its own firmware, which is separate from the mp3 player firmware and is installed in a chip on the back of the display. The display firmware can only be upgraded by pulling and reprogramming or replacing the firmware chip. It is not downloadable like the mp3 player's firmware. The main motivation for this beta test is because the display's firmware isn't easily upgradable. If any bugs do turn up in the firmware, we'll provide replacement chips for $6 each for anyone who doesn't have an EPROM programmer (that can accept 32 pin PLCC chips). At the moment the mp3 player firmware only prints the filename as it starts playing, but it's easy to work with the display using printf, so more interesting support for the display in the mp3 player's firmware should not be too difficult. May 27, 2001: I added support to the display board for its 12 pushbuttons. There are still a couple minor known bugs to fix on the display board, but they're easy to fix, so it's quite likely we'll be shipping beta test boards next week. I'll post an update when the beta-test display is an orderable part. I did quite a bit of debugging on the player's firmware. I also switched the serial driver to use interrupts, and started the timer drivers (still not working yet). Monday is a holiday, and I'm planning to spend most of the day on this project, so there'll be another update here on Monday night. The yahoo group is working out quite well (thanks Russ), so if you're not on the group yet, it's probably a good way to get involved in the project or at least keep up with what's going on. May 20, 2001: I hacked on the code all weekend, and I finally fixed the bug that was keeping the player from playing more than just the first file. I also did quite a bit of work on the display, and at long last it's (mostly) working. There is only minimal support for the display in the player's firmware at this point, but here's a photo of what it's doing today:

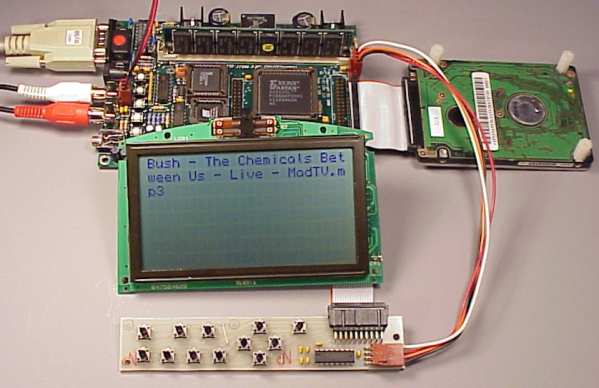

The display board actually has an 8051-based system on the back side, and the firmware that runs on the display board may be found in the 0.6.2.5 source code. When you build the code, the makefile will create "lcd.hex", which is the code that runs on the display board itself. "lcd.hex" is about 95% complete. Unfortunately, the JW-002 doesn't support flash upgrading, so you need to use an EPROM burner to program the display's firmware. The boards we'll sell (hopefully very soon) will have the firmware already installed, but to upgrade will mean a chip swap. "lcd.hex" only needs to have debounce and reporting code for those 12 pushbuttons added inside a timer interrupt routine. So far it's working pretty well, as you can see I just got the bugs worked out of the C to asm (drivers) interface, so the player's "main.c" able to do what the assembly code was able to do before. Using the display from the firmware is easy, now that the C-based firmware has the printf() function. It's just a matter of calling printf with the a couple display control bytes and the message to show. Inside 0.6.2.5's main.c, on line 202 is the printf that printed that filename on the display. At this point, the larger picture is still a bit more work to do on the drivers to fill in missing functions needed for really cool features (timers, file_uncache, buffered serial I/O), and just a bit more work on the display's code to allow those 12 pushbuttons to cause messages to be sent to the player. If you've been considering hacking on the project, but waiting for it to convert to C, now's the time to grab 0.6.2.5 and take a peek. You'll also need the very latest version of SDCC from CVS, as Johan fixed a bug just yesterday that allows SDCC to compile part of the code, and earlier in the week a critical (for using the display) bug in SDCC's string handling was also fixed. AS31 is also required, and the setup of all this stuff is easiest on a linux system (if anyone gets it to build under windows, please contact me with details). Not all of the system calls needed for really cool features are available yet (particularily file_uncache and timers), but they will be soon. The C code is now stable enough to try for some fairly complex features. The next thing I'm going to work on is getting the last bit of code onto the display board, so that the 12 pushbuttons will be able to send commands to the player. May 9, 2001: I fixed more bugs in the conversion to C, and now the firmware can actually play the first file! Of course, problems occur on the second one, but still it's pretty exciting to get the C version to start working. I should write a bit about the display. The basic news is that I'm embarrasingly behind schedule. As you can see from the photo of exactly one month ago, the hardware is more-or-less ready to go, but as always, there's more work to be done firmware-wise. There's actually two firmwares. There is the firmware that runs on the display board itself, which isn't easily upgradable. That firmware basically implments the communication protocol to receive commands from the mp3 player, like "move the cursor to this position" or "print this string". Except for getting the change of state on the pushbuttons into the protocol, the firmware for the display board is complete. What's so far behind schedule is getting the firmware for the mp3 player itself to send useful commands to the display board. Most of this code will ultimately be written in C, so it seemed like such a waste to write a bunch of that code in assembly and then discard it in the upcoming conversion to C. If you look compare 0.6.2 to 0.6.2.4, the first 870 lines of assembly in "player.asm" were removed and re-written as about 260 lines of C code in "main.c" and 50 lines in "startup.c". While it does delay the project, this conversion to C really is needed to be able to handle a more complex user interface. I'm pretty good with assembly, but not that good! Russ created a message board at Yahoo Groups, dedicated for this project. If you're interested in chatting with other users, give it a try. Please don't fill the message board up with questions like "when will xxxxx be ready?" May 6, 2001: I've spent almost all weekend playing with SDCC and converting the main program portion of the code from assembly to C. That's the easy part, really. The hard part is creating function prototypes for all the existing code that's going to remain in assembly, and making the "glue" code that allows the existing assembly code to be called from the C program. Some other ugly issues I've been putting off, like properly responding to interrupts with the banked code memory also had to be addressed. So far I've got fifty functions defined to tie the existing drivers and filesystem code to the C application, and most of them actually work. At this point, I've got the C application more or less written (functionally the same as 0.6.2.1), and it sort-of works after much debugging. Saddly, there's only so many hours in a day. In the spirit of ESR's "release early, release often", I put the code in its present state on the firmware page. I only posted the source, not a ready-to-use image file, because it really doesn't run just yet. Still, if you've been following this project and want to get your hands dirty (but not assembly-language dirty), take a peek at the C code. It's all in "main.c" right now, and it's only a few hundred lines of code to read (a lot easier than trying to make sense out of more than 9000 lines of assembly!!) May 3, 2001: This evening I finally put Tom's parameter storage code to use (after some edits to it). Version 0.6.2.1 stores the volume setting as a non-volatile parameter. It should be easy to add more settings to the non-volatile storage, like the file that was last played and the random number "seed", but at the moment only the volume setting is stored. May 2, 2001: I just put version 0.6.2 on the firmware page. Version 0.6.1.E has turned out to be quite stable, so I'm planning to call 0.6.2 "stable", unless I hear reports of significant problems in the next several days. The main change in 0.6.2 is proper support for using the board without a SIMM. Apr 22, 2001: Quite a lot has happened since my last update two weeks ago. We finally have more assembled boards in stock. They are "Rev B" boards, with a minor change in the power supply. The change makes the input range of the 2-pin connector 6 to 10 volts, instead of 4.5 to 6 volts. The advantage is that the power supply isn't easily damaged to applying too much voltage (say 12 volts to the 2-pin connector), and the TIP102 transistor doesn't run nearly as hot when the board is powered with 14-15 volts on the 12 volt input. For battery operation, six AA cells are needed with the Rev B board, instead of just four. I'm behind schedule with the display board beta test. I had wanted to send out beta test boards two weeks ago, but a week of travel and meetings put me a week behind with Veris (the day job, this MP3 player is in my off hours), so I didn't manage to do much with the MP3 player project in the last couple weeks. It's looking really good that it's actually happen this week. Also planned for the near future is a page with much more detailed info about the display board. It's always risky to make promises, but at the very least I will be working on this project this week and this page ought to get a couple updates through the week. A group of students at BYU did some work to try to add ATAPI device support to the firmware. They wrote these seven web pages about their project. The work is incomplete, but it looks like they did have some success implementing some of the low-level code. I know of one other person who's interested to try and implement support for ATAPI devices. Eventually this code could lead to support for CDROMs. For now, I'm going to stay focused on getting the display board working and on display and navigation features in the firmware. When the display stuff is mature, I'll probably look into this ATAPI/CDROM support, but I will of course accept patched in the meantime :) I also managed to get a USB Adaptor Board recently (from www.in-system.com, who has been acquired by Cypress Semiconductor and their old website has vanished) It's quite a bit smaller than the one shown in that photo. It's about 2.5 by 1.5 inches (6.4 by 3.8 cm), with the USB connector on the opposite side of the board. I haven't had time to do any testing with it, but it looks like it ought to be possible to get it to work with the player. The trick is to have it tell the player when the USB is active and have the player not attempt to talk with the drive. These boards are about $42 in single piece quantity, which is a bit more expensive than I'd like, but maybe that's ok? Apr 9, 2001: This weekend I made display adaptor board layout and etched three prototype boards. Here's a photo of one of the boards with a new display (still has the blue protective coving):

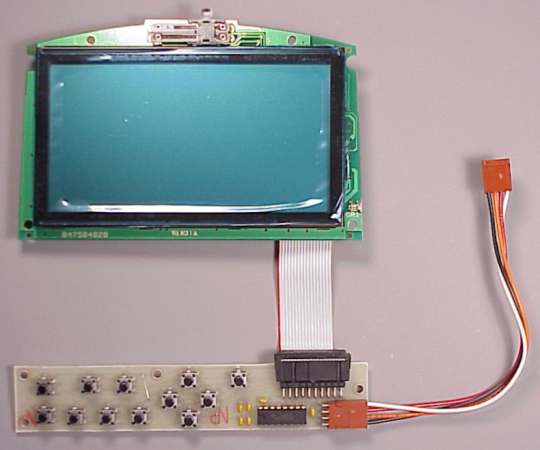

I actually wanted to be at this point on Saturday, as the firmware still needs a bit of work. I wanted to ship four beta test boards on Monday... it's really close, as you can see from the photo, but just a bit more work is needed in the code that goes in the chip on the back of the display board. The bad news is that it's not looking too good for getting much done on this project through the week. Tuesday is dinner I need to go to, and I'm flying out on Wednesday afternoon to visit a (Veris) customer on Thursday. It may next weekend when I can finally ship the beta test boards out. I made three tonight, and I'll probably make 3 more, and so far I've heard from 4 people who want to give these boards and the first firmware a try. Of course, we'll have some nicer "professional" boards made in a couple weeks, with the usual green solder mask, silk screen, and plate-through holes. It's looking like we're going to sell a kit with all the items shown in this photo, for $47. That's the display board itself, with a firmware chip installed that has the firmware needed, the 17 pin ribbon cable (attached to the board's connector), the adaptor circuit board with 12 pushbuttons, and the 4 pin cable to connect to the mp3 player. It's also possible to buy the display board from Earth Computer Technologies ($39), if you want to program an EPROM with the firmware and build your own adaptor board and cables. Soon I'll add a page with quite a bit more info about the display, including the firmware source code needed to make it work. Apr 3, 2001: Here's a little image I drew that shows approximately what I'm planning for the display adaptor board. The scale is 100 dpi, so the planned board size is 5.5 by 1 inch (14 by 2.5 cm).

On the right side is a ribbon cable connector that will connect to the display board itself, and a 4 pin molex header that is a right-angle version of the one on the right side of the mp3 player. The design allows for 12 pushbuttons. The exact function of each pushbutton will be determined by the mp3 player's firmware, not the hard-to-upgrade firmware of the display board. Though not shown in the diagram, there ought to be space to put 12 pairs of holes so allow off-board pushbuttons to be easily connected. At this point, the big question is how to arrange the pushbuttons on the board? This drawing shows one possible scenario. I added the green text to illustrate some potential functions for the buttons, but keep in mind that the exact functionality of each button is due to firmware in the player, not the design of this board (which is what I'll be concentrating on this week). If you have any opinions or insights about how these buttons might be well arranged, now would be a really good time to email, but please please please, try not to get caught up in all sorts of complex details about menu systems, playlists, etc. All that sort of stuff is to come in the mp3 player firmware, but after this board is finished. Apr 2, 2001: This weekend Robin and I built up a few mp3 player boards from the extra parts we had. So the good news is that everyone who was waiting for a board (with a valid order) is getting a board shipped today. At the moment, we have just two boards left, and a small handful of invalid orders (shipping cost confirm req'd and not received, declined credit card, check/money order not received, etc). We also built up more of the 8051 boards, which means we're not in danger of running out of those and getting into this time-consuming business of trying to be fair about who gets the last few boards. (we should have plenty more mp3 player boards in about 2 ½ weeks). On LCD display board front, I've been having trouble actually getting a good number of them. On Friday I was told that a box of them is being shipped, so hopefully we'll have some to offer soon. We're planning to sell the display board a little kit, which will include the display circuit board with a ribbon cable attached, and a firmware chip installed to implement the command set. The kit will also include a little adaptor board that has 12 pushbuttons, a connector for the ribbon cable, and a 4 pin connector that's the same as the one on the right side of the board. Of course, we'll include a short 4 pin cable to connect between the boards. The adaptor board is simple, it's just one MAX232 chip and some capacitors and the pushbuttons. The MAX232 converts the serial signals, and provides a negative voltage which is needed for the LCD display. That little slide adjust on the top of the display allows the contrast to be changed, and the negative voltage from the MAX232 is enough for the right most setting to be really dark. I don't have all the costs added up just yet, but unless it means losing money, I really want to sell this display kit for under $50. It will also be possible to buy the display board itself, without the firmware installed and without the adaptor board and cables, directly from the vendor (qty=1). I'll post a page with more info about this, including the firmware source code and instructions to do-it-yourself, probably next weekend (if I actually receive the package this week). The display board I currently have, shown in the photo on March 7, has many mods on the back side for firmware development and other hacking, so it isn't a good example for testing and explaining what we'll actually be able to sell. My short term plan is to build up a few kits with "beta test" firmware, for a few adventerous souls who'd like to try the display right away (I have 4 people on my list so far, email if you're interested). Unfortunately, the display board isn't easily firmware upgradble. The firmware is in a PLCC socket and requires swapping the chip. It isn't downloadable like the mp3 player board. I have the firmware more-or-less finished (still a bit to do with the pushbuttons), but it's always possible that there's a bug or two, so I want anyone who buys one of these boards early-on to understand that they may need to pull the chip and reprogram it (we'll use flash on the first boards), or get a new chip if an eprom programmer with PLCC socket isn't readily available. In the long run, my plan is to keep the display board firmware simple and avoid adding features to it, and instead add fancy features into the easily upgraded mp3 player firmware. On the firmware front, I haven't heard any complaints about the out-of-memory bug with 0.6.1.E. I ran it for quite a while and I've been seeing some warnings from the memory allocation routines, which may not be a big deal as nothing bad seems to be happening. I'm starting to think that some of the problems I was seeing may have been due to damage to my board's power supply (that board with the yellow dot has seen a lot of abuse thoughout this project, which is why it has a yellow dot... so we don't ever accidentally mistake it for a new board that we would sell). There obviously is a need to do a bit of clean up in the code before a 0.6.2 release. As you can tell from reading this page, I haven't had much time to do much with the firmware in the last couple weeks. It looks like we've done just about everything we can do with getting more boards built and be fair and satisfy everyone who's been waiting, so hopefully I'll be able to get some real work done on the firmware and LCD board in the next week or two. The Rev B circuit board will have some minor changes in the power supply, which result in the lower voltage input connector having a range of 6 to 10 volts. A couple of people have been unhappy hearing about this change, so maybe it's worth taking a moment (in this already too-long update) to explain the change and the motivation behind it. It was my hope that the change would provide a 4.5 to 10 volt input range, but that didn't really work out. The new circuit will actually run a bit lower than 6 volts, but not near 5 volts. The biggest advantage of the change is that the low voltage input isn't easily damaged if you apply 12 volts. I had a couple people return boards with the 74AC14 chip blown, which was almost certainly due to applying a higher voltage to that input. The 74AC14 has an absolute maximum of 7 volts (though they will sometimes survive more... sometimes). In some cases, the 74AC14 will blow in a way that allows the supply to temporarily output too much voltage, which causes the FPGA or STA013 to also fail. The new mosfet driver chip can handle 14 volts. The 10 volt limit is due to the capacitors, though they can usually take a bit more voltage without trouble. Making the board more sturdy to abuse was a big concern for me. The other advantage of the higher voltage input range is that the linear step-down preregulator (TIP102 transistor) will have less voltage across it. When the board powers a laptop drive, this TIP102 part runs hot. It's still within its spec, but it can get very hot to the touch, particularily with a laptop drive that draws a bit more current. The original idea was that the hard drive would never spin for any long period of time thus limiting the temperature rise... but has you can see from the history of these updates, that has turned out to be easier said than done, with the 0.6.x firmware still not completely debugged enough to be called "stable" (though 0.6.1.E is pretty good). As far as motivation behind the design, the linear preregulator was done for two reasons... originally to allow a power supply I first designed for batteries to run from 12 volts, and to provide protection from the 60 volt spikes that will happen in a car if the car's battery is disconnected while the engine is running (I didn't want to have a fuse that blows). I originally wanted to run from four NiCd cells. It's looking like the 0.6.x firmware can run for 5-6 hours from four 1500 mAH NiMH batteries (available from Radio Shack), using the 0.6.x firmware and 16 meg simm... which is quite a bit better than Creative Lab's Nomad Jukebox! This new design will need six cells instead of four. I know that's a bit heavier and bulkier, but since the board is 5.75 by 4 inches (14.6 by 10 cm) due to using through hole components that hobbists can easily solder, the extra two batteries don't seem so bad, and the play time will be longer. The larger voltage range also means that alkaline batteries may have a chance, though NiCd or NiMH are much better at suppling the large current needed to start the laptop drive motor. For the distant future, one interesting idea I've heard is to actually build two separate 5 volt supplies, one for the drive and one for the board. This would be a major redesign, but the idea is interesting because then each supply could be designed and optimized for just its expected load range, instead of the current (difficult) design which needs to handle such a large range of load currents, and the supply dedicated to the drive could be completely shut off. I'm intrigued by this because it turns out that laptop drives draw a significant current even when in full sleep mode. My Hitachi DK23AA-12 drive measures 17 mA in full sleep. If anyone out there reading this is a switching power supply guru, I'd be interested to hear from you, particularily about how to get 5 volts at 1.2 amps from a 4 to 15 volt input (SEPIC, perhaps? ... currently using flyback). Well, for now I think the Rev B board will be a minor improvement, and if you really wanted to run with a 4.5 to 6 volt input, well, I'm sorry (though we have two assembled boards and a several kits left as of today). Mar 28, 2001: It's been a while since I updated this page. We ran out of the assembled mp3 player boards. I've been spending most of my project time working on getting the next batch of boards ready. I did end up making a minor change to the power supply, which turns the low voltage input range from 6 to 10 volts, instead of 4.5 to 6 volts. It's looking like we'll have the new bare boards next Tuesday, and then it's a two week process to get the boards assembled (it can be done faster, but the cost goes up sharply). This last week has been a not-so-fun job of counting all the parts and ordering the ones we're missing, which really isn't very interesting, but I thought I'd put an update on this page anyway. The processing of orders is usually pretty simple, but it gets complicated when we're almost out of stock. We also happened to run out of the 8051 development boards at about the same time, doubling the number of orders that need special attention, but those are fortunately back in stock again. Robin has been out of town most of this week, and I'm not nearly as good at it as she is (and I don't end up getting much done on the firmware). Well, with a bit of luck the last pending orders will be completed or canceled and we'll offer the boards to others who are waiting, and the board assembly will go smoothly over the next two weeks. Mar 19, 2001: I spent quite a bit of time playing around with tweaks to the power supply. Today the 2-pin connector on the right side of the board accepts 4.5 to 6 volts. I really wanted to widen the range to 4.5 to 10 volts (for Rev B boards), but it's looking like I managed to make it about 6 to 10 volts. I'm not so happy about not being able to run from 5 volts, which is such a common regulated power supply as well as 4 NiCd batteries. I'll probably do a bit more fiddling. Maybe 6 to 10 volts is ok? I received a bug report about as31, though it was the S-Record output format, so it doesn't effect this project which is based on Intel-Hex format. I did fix an annoying problem where the command line version wasn't returning error codes to the shell, which causes "make" to continue building when it should stop. If you're building the project from the source, be sure to grab this new version of the AS31 Assembler. Mar 18, 2001: I spent yesterday and this morning working on the display firmware. Most of the features described on the LCD protocol page are working now. I added more details to that page as I wrote the code for each part. This morning I got the scrolling to work. I also built a little prototype board with 12 pushbuttons. The display board firmware reads the buttons (3x4 matrix, 7 I/O lines), but a bit more work is needed for up/down detect, auto-repeat, and support in the protocol. I'm not sure exactly what functions will ultimately get programmed to the buttons, but the display board adaptor will be able to provide 12 buttons. I suppose 4 want to be for 2-dimentional cursor/selection movement and 1 for enter. The existing 6 buttons probably want to be duplicated, except random mode may turn into a menu choice. Right now the big question isn't exactly what to do with each button, but how to arrange them on the board that will fit just below the display. The 4 buttons for up/down/left/right probably want to be in a diamond shape. I'm imaging that this board will probably be about 1 inch high by 5 inches wide (2.5 by 10 cm), and a portion on the right side will be taken up by connectors and 1 chip. We're nearly out of boards. I've been putting off ordering more circuit boards, because I wanted to make some minor changes to the power supply on the next round of boards. The main change I've wanted to make is to replace the 74AC14 with a proper mosfet driver chip. I spent the afternoon tweaking a TPS2814 chip onto a board. That's the easy part... the hard part is that two of the inverters from the 74AC14 form a software shut-off circuit. The idea is that the firmware can turn off the power supply (the play button wakes the power supply up). I've never really done much to support this from the firmware. There's very little extra space left on the board and many attempts to build another shutdown circuit were not successful, so maybe I'll just leave the board as it was, with the 74AC14, or maybe I'll change to the TPS2814 and abandon the shutdown circuit. I did some playing with a LMC7211 comparator to make a shutdown circuit, and it's looking like it just might work. It's a SOT-23-5 surface mount package, and I've tried to avoid surface mount to keep the board easy to assemble from the kit. Everything's a trade-off, I guess, but these really are pretty minor tweaks to the power supply. Well, one way or another, I really need to order boards on Monday or Tuesday, so I'll have to make a choice and go with it for the next batch of boards. Mar 16, 2001: I'm going to try releasing beta test firmware very frequently, starting right now. I just put 0.6.1.E on the firmware download page. This version fixes the no-sound bug. There is still one major bug left, which I'm calling the out-of-memory bug. Eventually, something goes wrong in the memory manager and usually this results in a significant memory leak, which you'll see in those message about how much memory is available after each file is finished playing. In some rare cases, memory pages will get mis-managed in some way the triggers one of a few sanity checks that will abort the player and produce a very long dump of critical memory areas. If you're watching with a terminal and happen to capture one of these giant memory dumps, please email it to me. My hope is that releasing beta test firmware frequently will allow you to keep up with changes in the project and try out the very latest code, if that interests you. I could also use more feedback out how they're working, but please keep in mind that a bug report is much more valuable if you can reproduce it with the debug messages turned on and capture them to a text file attached to your email (type "DEBUG", or edit the code and uncomment "setb debug"). The only potential downside is that our little site has limited bandwidth and quite a number of people run those abusive archiver programs (Teleport Pro, WebZIP, etc). If this gets to be a bandwidth problem, I'll probably start removing older beta versions that aren't of much interest. Mar 15, 2001: It's looking like I may have finally solved the no-sound problem that happens with some boards. It turns out that the STA013 MP3 decoder chip requires a bit of time to initialize itself after a reset. The tricky part is that there is a code burried deep within the config file provided by the manufacturer (ST) that does a soft-reboot. They don't document this anywhere, and it's not mentioned in the suggested algorithm for sending the config data. I added a 0.6 ms delay into the downloading just after any writes to register address 16 (the soft reboot register), and this has completely fixed the no-sound problems on the board I have that reproduces this problem regularily. I emailed firmware images to the four people who've reported this problem recently, so hopefully I'll get some feedback about how this change effects their boards. If you have a board that sometimes boots up and produces no sound but says it's working, please contact me and I'll email you this firmware file. Feedback is really valuable with these hard-to-reproduce problems. Hopefully this no-sound issue will finally be fixed. Mar 14, 2001: Once more, I've fallen a bit behind on updating this page. I did quite a bit more work on the display firmware and fonts. I create this page with the LCD's fonts and another page with the planned communication protocol for the display. I still need to write quite a bit of the code for the protocol. That's probably happen this weekend. I'm hoping to have a good idea of pricing for these display boards by next week. I'm planning to have some small adaptor boards and cables to allow it to easily plug into the MP3 player and also provide remotely mounted pushbuttons. It'll take a couple weeks to get these boards and custom cables ready. If you're impatient and want to get a display as soon as the firmware is ready (and build your own cables and adaptor board), contact me by email. Recently I've been putting quite a bit of work into solving the no-sound bug that happens with a small number of the boards. Some times the MP3 decoder chip doesn't get properly initialized, or at least that seems to be what's happening. Most boards only very rarely have this problem, if at all, but a few boards do it much more regularily. Last night I finally managed to write some code that can reliably detect when the chip isn't properly initialized and it retries. Each retry takes about 2.5 seconds, and it seems to eventually get the chip initialized properly. I'm not happy with such a kludge, so I'm still working to try and find out exactly what causes the improper initialization, but at least this retrying allows boards to work properly. If you have a board that does this no-sound problem, please email me and I'll send you the latest beta-test code. Mar 7, 2001: I haven't posted here in a few days. Last Thursday I got a LCD display, which looks like a good choice for this project. It's 8 lines by 24 characters and includes an 8051 based system on the back side, so very little extra hardware will be needed to make it work. It's new (unused) from a surplus supply vendor, and it came without working firmware or any significant docs. They've got a very reasonable price on them, considering that it's got a complete 8051 system on the board and the display area is large, about 4 inches wide by 2 inches tall (5 by 10 cm). That's just the active area of the display, the board itself it only slightly smaller than the MP3 player board. Here's a photo: